Evaluation von Undervolting auf LP FPGAs

- Typ der Arbeit: Masterarbeit

- Status der Arbeit: abgeschlossen

- Betreuer: Ulf Kulau

- Bearbeiter: Lucas Bublitz

- Ende der Arbeit: 30. Oct 2022

Energieeffizienz spielt eine immer größere Rolle, insbesondere für kleine ressourcenbeschränkte Systeme wie bspw. Sensoren. Eine Methode um die Leistungsaufnahme zu reduzieren ist Undervolting, bei dem die Processing Unit unterhalb der spezifizierten Spannung betrieben wird. Für Mikroprozessoren wurde Undervolting bereits erfolgreich implementiert und es hat sich gezeigt, dass eine enorme Steigerung der Energieeffizienz (bis zu 42% bei einem ATMega1284p) erreicht wird. Für Smart Sensors ist neben Mikroprozessoren aber auch der Einsatz von LP (Low Power) FPGAs eine spannende Alternative für die Signalverarbeitung. Auf dem FPGA lassen sich spezielle Hardwarestrukturen umsetzen, kleine Softcores implementieren oder dedizierte Beschleuniger für rechenintensive Tasks umsetzen. Genau diese FPGAs sollen nun eingehender auf ihr Verhalten unter Undervolting untersucht werden.

FPGAs bieten per se keine Möglichkeit von Energieeffizienzmechanismen, wie bspw. Sleep-Zustände auf Mikroprozessoren. Viel mehr kann in einem FPGA alles implementiert werden was sie einerseits sehr flexibel macht, anderseits aber auch zu Lasten der Energieffizienz geht.

Undervolting könnte hier eine sehr gute Basis darstellen, weitreichende Energieeffizienzmechanismen für LP FPGAs zu implementieren. Sei es ein effizientes Deep-Sleep oder mittels asynchroner Rechnerstrukturen. In dieser Arbeit sollen grundlegende Untersuchungen an LP FPGAs und Undervolting ermöglicht werden, als Basis für weiterführende Forschung.

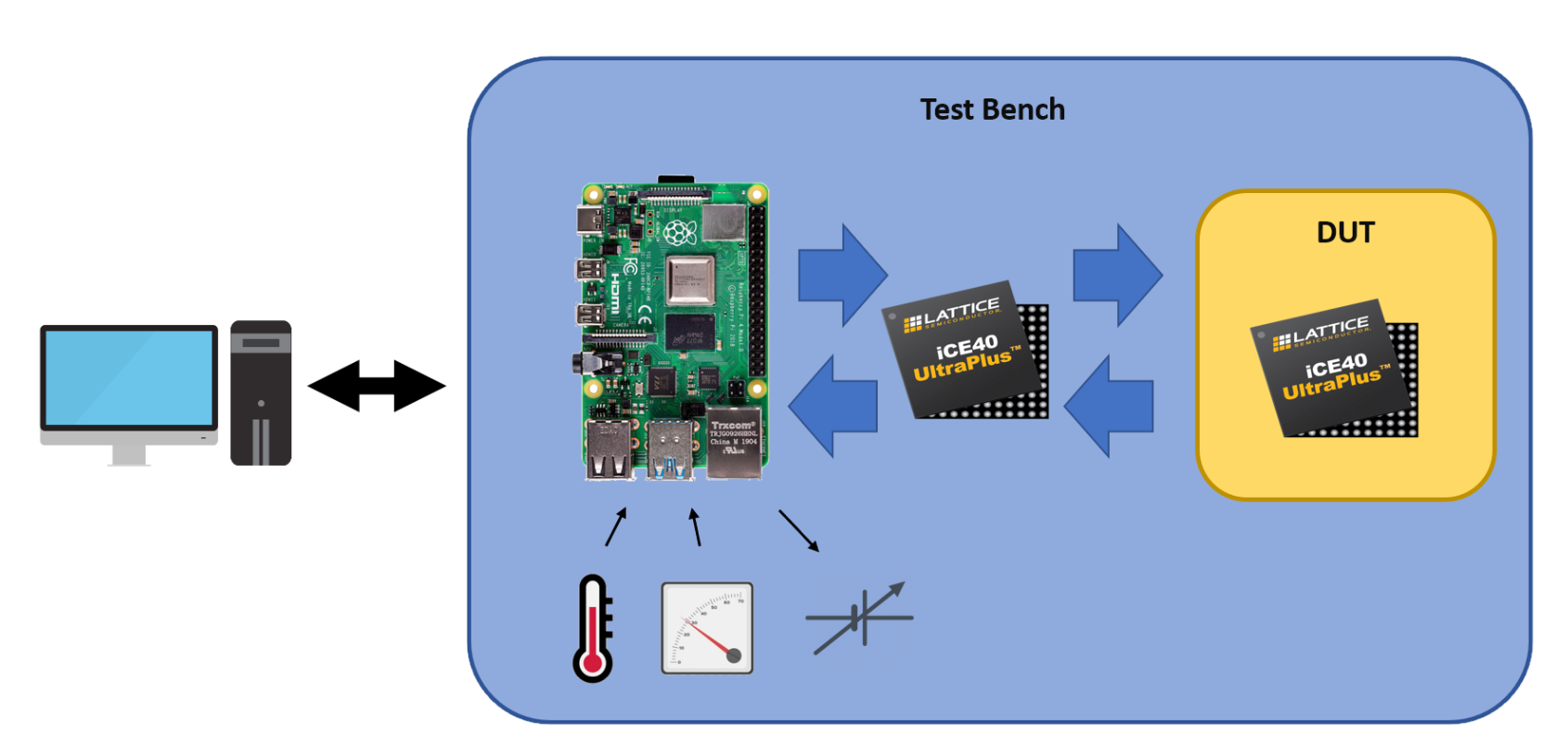

Konkret sollen LP FPGAs der Familie Lattice ICE40 untersucht werden, da diese häufig auf ressourcenbeschränkten Systemen zum Einsatz kommen und es für diesen Typ von FPGA eine Open Source Toolchain gibt. Für die ICE40 soll eine Testbench entwickelt werden, welche das automatisierte Testen von einer signifikanten Anzahl von FPGAs ermöglicht und die Orchestrierung und Wiederholbarkeit von Testreihen vereinfacht. Neben der Möglichkeit die Versorgungsspannung des DUT (Device Under Test, hier die FPGAs) präzise skalieren zu können, sollen Parameter wie Spannung, Stromaufnahme, Temperatur parallel zu jedem Test erfasst werden können. Um das DUT eingehend testen zu können, müssen ferner die GPIOs ausgelesen werden können, bspw. um Testvektoren interner Fehlererkennungen auszuwerten. Die Testbench selbst muss eingehend evaluiert werden, damit diese als Valide Grundlage für weiterführende Tests genutzt werden kann. Im Anschluss sollen Teststrukturen auf einem FPGA implementiert werden und dessen Verhalten unter Undervolting mittels der Testbench ausführlich evaluiert werden. Für die Masterarbeit ist es obligatorisch, dass verwandte Literatur untersucht und in die Bearbeitung einfließt.

Tasks

- Einarbeitung in das Thema Undervolting auf LP FPGAs auf Basis verwandter Arbeiten (Related Work)

- Entwicklung einer geeigneten Testbench in Hard- und Software zur Untersuchung von Undervolting auf ICE40 FPGAs

- Evaluation der Testbench hinsichtlich ihrer Eignung für weiterführende Untersuchungen

- Implementierung und Untersuchung von Teststrukturen auf den ICE40 FPGAs und Durchführung einer Testreihe (Evaluation)

- Dokumentation der Ergebnisse

Further Reading

-

-

WFIoT

Conference

Undervolting in WSNs – A Feasibility Analysis -

IEEE World Forum on Internet of Things 20142014.

10.1109/WF-IoT.2014.6803228 [BibTex]

-

WFIoT

Conference

-

-

TOSN

Journal

IdealVolting – Reliable Undervolting on Wireless Sensor Nodes -

ACM Transactions on Sensor Networks (TOSN)12.2ACM2016.

10.1145/2885500 [BibTex]

-

TOSN

Journal

-

-

EnsSys

Workshop

DUO: Integration of Dependable Undervolting in Operating Systems -

Proceedings of the 7th International Workshop on Energy Harvesting & Energy-Neutral Sensing SystemsACM2019.

doi.org/10.1145/3362053.3363487 [BibTex]

-

EnsSys

Workshop