I3C Interface Implementation and IMU Performance Evaluation on FPGA

- Typ der Arbeit: Masterarbeit

- Status der Arbeit: reserviert

- Betreuer: Ulf Kulau

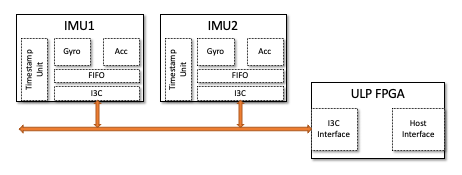

The I3C host interface is to be implemented on an FPGA. During the implementation, care should be taken to make the I3C IP core relatively generic so that it can be used in further projects. The I3C protocol can be very complex and supports many features. Since the Zeil platform is a resource-constrained FPGA, another focus of the implementation will be to decide which core functions must be implemented and which should be considered optional. Two identical IMUs (Bosch BMI323) are to be used as sensors. These sensors have an internal time stamping unit, so that sensor values can be tagged. Each IMU contains both a 3D accelerometer and a 3D gyroscope whose axes are to be read out.

The goal should be that the time difference between the axis values of one sensor, but also between all values (of both IMUs and both internal sensors) is as small as possible, in order to be able to merge the data in the best possible way.

For this reason, a performance evaluation should be performed. Here also the internal FIFO of the IMUs can be used to parallelize the data acquisition a bit. Overall, it will be intensively investigated which data rates and latencies can be achieved and how the I3C bus scales in the process.

The following figure illustrates the sensor system:

Tasks

Here is the task and description of the tasks in bullet points:

- Familiarization with the topic, setting up the toolchain and working environment

- Implementation of a simplified I3C host interface on a Lattice Ice40 LP FPGA

- Integration of two IMUs (Bosch BMI323) and use of FIFO and timestamping function

- Performance evaluation with focus on data rates, latencies, scalability and efficiency

- Documentation of the results (written elaboration)