Lightweight Testcore for Hardware Modules of LP FPGAs

- Typ der Arbeit: Forschungsprojekt

- Status der Arbeit: abgeschlossen

- Betreuer: Ulf Kulau

- Ende der Arbeit: 24. Feb 2023

Static Random Access Memory (SRAM) based Field Programmable Gate Arrays (FPGAs) are becoming increasingly popular in the space industry and IoT applications due to their in-field re-programmability, reconfigurability, and suitability for signal processing applications. When selecting an FPGA for space or IoT applications: reliability, low power, and low cost - come into the picture as driving selection parameters. Even though SRAM-based FPGAs have been in the market for the last few decades, it was not the researchers’ choice for space electronics due to their high susceptibility to space radiation. In space, radiation can negatively impact the reliability and performance of SRAM-based devices, as the bits of SRAM memory can get altered due to radiation exposure, resulting in Single Event Upsets (SEUs). Nowadays, as the FPGAs become more and more powerful and Application Specific Integrated Circuits (ASICs) become less cost-effective, in terms of non-recurring engineering costs, researchers are shifting their focus again to these SRAM-based FPGAs. Besides, while exploring different techniques to downscale the power consumption of an FPGA, undervolting is a powerful concept often exploited by researchers. Also, during undervolting an FPGA, bit-flips are prominently observed. So, making the FPGAs reliable against bit-flips is a prime research focus for the industry. Although mechanisms like Tripple Moduler Redundancy (TMR) have already proven effective in detecting and counteracting SEUs, they come with considerable device overhead. Again, if we think about resource constraint FPGAs, TMR is highly inefficient. As a result, researchers have been focusing on scrubbing-based methods.

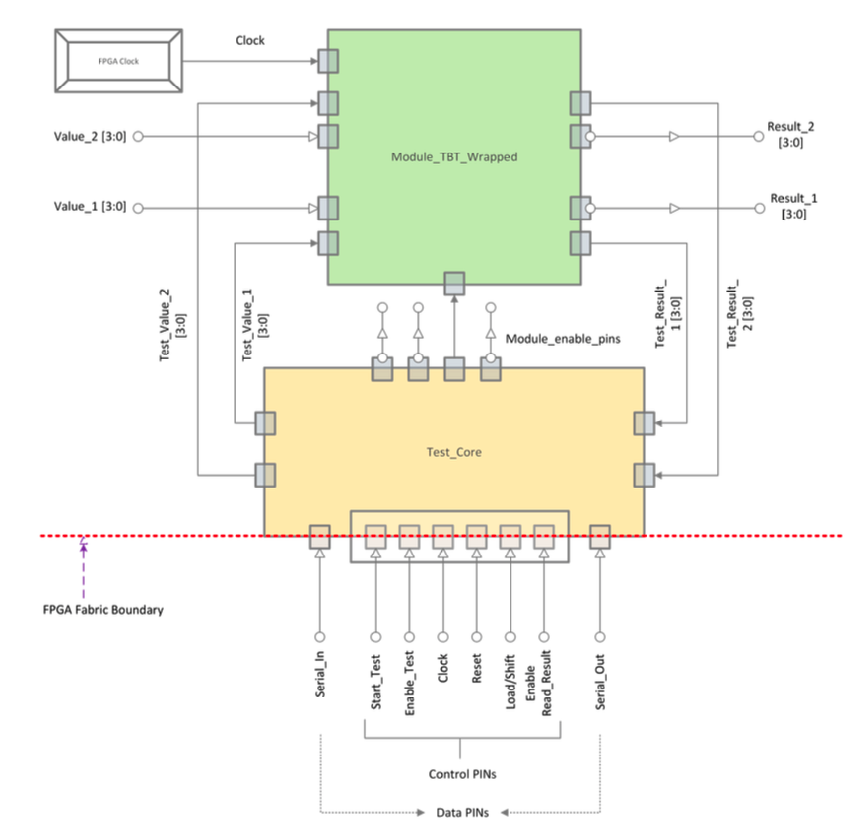

In this project, we focus on developing a lightweight hardware Testcore for FPGAs that we can utilize to detect these SEUs/bit-flips regardless of FPGA resource conditions and perform a blind scrubbing if an error is detected.

Tasks

- Familiarization with the topic of how defects can be detected (scrubbing)

- Development of a generic concept for testing hardware modules on an FPGA

- Implementation of the test core on the FPGA and on a MCU to perform the test

- Detailed evaluations

- Documentation of the results