Evaluation and Optimization of a Resource Constraint Test Core in Ultra Low-Power FPGAs

- Typ der Arbeit: Forschungsprojekt

- Status der Arbeit: laufend

- Projekte: AuRelia

- Betreuer: Kazi Mohammad Abidur Rahman

Before continuing please visit: Project Thesis

Motivation

Static Random Access Memory (SRAM) based Field Programmable Gate Arrays (FPGAs) are becoming increasingly popular in the space industry due to their in-field re-programmability, reconfigurability, and suitability for signal processing applications. When selecting an FPGA for space applications: reliability, low power, and low cost - come into the picture as driving selection parameters. However, the ultra-low power FPGAs, suitable for space and smart sensing applications, tend to become more and more resource contraint in order to reduce power consumption.

But lag of resources, specially different interfaces like JTAG, can eventually mean that the FPGA fabric is not testable once deployed. Usually, blind scrubing or periodic reprogramming is performed in space, which eventually cannot gurantee the data accuracy, making the whole process less reliable. In space, radiation can also negatively impact the reliability and performance of SRAM-based devices, as the bits of SRAM memory can get altered due to radiation exposure, resulting in Single Event Upsets (SEUs).

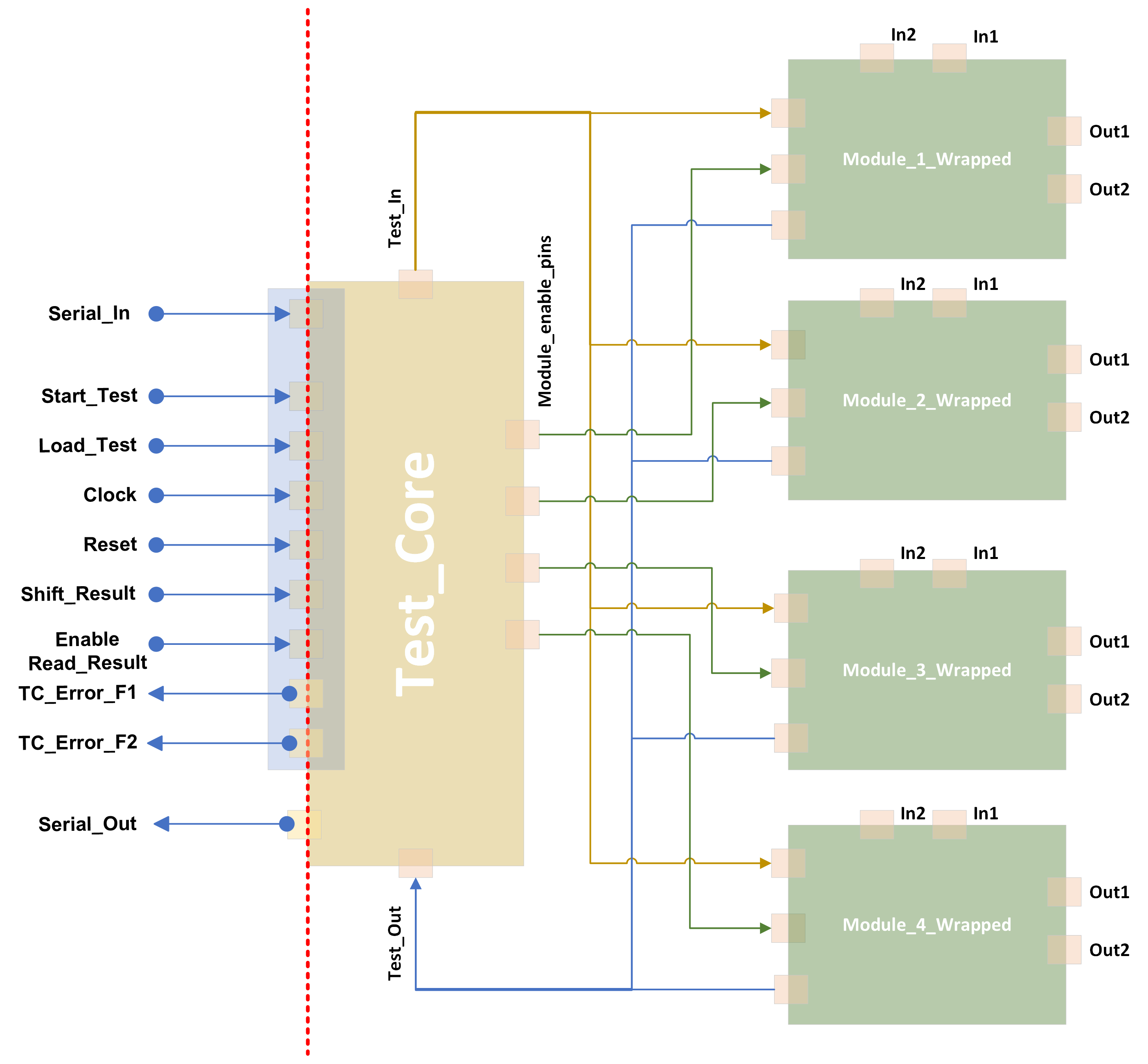

To encounter such problems, a resouce-constrant, highly reliable and universal Test Core mechanism can be a solution. In this thesis project, we will focus on investigating a Test Core developed by Smart Sensor Group. This will involve understanding and evaluating the test core in terms of resource and energy, resource optimization and fault injection.

Tasks

- Get familiar with the test core

- Implement different signal processing blocks in verilog

- I/O Optimization

- Evaluation

- Documentation

Further Reading

- iCE40UltraPlus

- nRF52840 Product Specification

- Yosys

-

-

DCOSS

Conference

ISFD: Efficient and Fault-Tolerant In-System-Failure-Detection for LP FPGA-Based Smart-Sensors in Space Expeditions -

2024 20th International Conference on Distributed Computing in Smart Systems and the Internet of Things (DCOSS-IoT)2024.

10.1109/DCOSS-IoT61029.2024.00021 [BibTex]

-

DCOSS

Conference